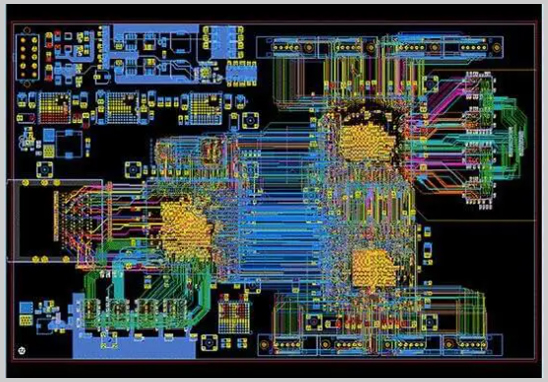

作為專業(yè)的PCB設(shè)計(jì)公司,宏力捷電子在長期的實(shí)際項(xiàng)目中�,總結(jié)出16條在實(shí)際工作中必須嚴(yán)格遵守的PCB設(shè)計(jì)原則。這些原則不僅有助于提高設(shè)計(jì)效率����,更能大幅降低返工、EMC失效�����、信號完整性等風(fēng)險(xiǎn)�。

不管你是設(shè)計(jì)2層板�、4層板����,還是高達(dá)12層的復(fù)雜多層板,這些原則都值得一看:

1. 高速信號盡量走內(nèi)層(夾層)

高速信號如USB�����、HDMI���、DDR等���,建議走在電源層或地層中間的信號層上,有助于控制阻抗���,降低EMI(電磁干擾)���。

2. 時(shí)鐘線優(yōu)先考慮布線順序

時(shí)鐘線是干擾源,也易受干擾�,應(yīng)優(yōu)先布線,保持最短�、最直、等長走線,避免分叉�����、繞行�。

3. 差分對走線保持間距和長度一致

如LVDS、USB��、CAN等差分信號�,要求兩條線長度一致、間距一致�����,避免串?dāng)_和信號失真�。

4. 電源與地線要寬�,形成完整地平面

電源線和地線應(yīng)盡量加寬,降低阻抗�����。地層建議整層鋪滿����,避免分割,減少回流路徑問題���。

5. 關(guān)鍵信號應(yīng)遠(yuǎn)離板邊

板邊是EMI敏感區(qū)��,避免高速信號靠邊布線���,尤其是BGA或高速連接器附近的信號更應(yīng)重點(diǎn)保護(hù)����。

6. 走線避免直角���,推薦用45°或圓弧

直角走線容易造成阻抗不連續(xù)��、信號反射�,盡量使用斜角或圓角處理轉(zhuǎn)彎處����。

7. 布線寬度和走線間距符合工藝要求

一般推薦走線寬度≥4mil,走線間距≥4mil����,但應(yīng)根據(jù)PCB廠商制程能力設(shè)定,BGA區(qū)域要特別注意���。

8. 高速線避免穿越分割區(qū)域

尤其是差分線或高速信號���,不應(yīng)穿越不同電源區(qū)域��,避免信號回流路徑斷裂���,造成信號完整性問題。

9. 去耦電容靠近芯片供電引腳

電容要盡量靠近電源輸入引腳放置�����,以減少電源噪聲和高頻干擾�。

10. 盡量減少過孔數(shù)量

過孔會(huì)引入寄生電容和寄生電感,破壞阻抗連續(xù)性�����,差分對走線過孔必須匹配�。

11. 模擬與數(shù)字信號分開布線

模擬信號對干擾極其敏感���,應(yīng)遠(yuǎn)離數(shù)字信號走線��,并做好地層隔離�。

12. 注意層間堆疊結(jié)構(gòu)對阻抗的影響

合理設(shè)計(jì)多層板的層疊結(jié)構(gòu),有助于阻抗控制和信號完整性��,常見疊層為:信號-地-信號-電源��。

13. 為測試預(yù)留測試點(diǎn)

測試點(diǎn)方便后期調(diào)試與維修���,特別是關(guān)鍵控制信號���、電源和地信號建議加上測試焊盤。

14. 元器件布局遵循模塊化

按功能分區(qū)���,電源區(qū)����、MCU區(qū)����、接口區(qū)等清晰劃分,有利于信號清晰����、干擾最小。

15. 考慮加工制造的可制造性(DFM)

設(shè)計(jì)時(shí)要考慮工藝邊距���、打件空間����、焊接裕量等加工可行性,避免設(shè)計(jì)無法落地�����。

16. 預(yù)留EMC/EMI整改空間

可在板上預(yù)留電磁屏蔽區(qū)�����、電容/電感濾波焊盤��,以應(yīng)對后期EMC測試整改需要�。

PCB設(shè)計(jì)是一項(xiàng)既講究理論,又強(qiáng)調(diào)實(shí)踐的工作�。尤其是在如今多層、高速�、微小封裝成為主流的背景下,設(shè)計(jì)者不僅要懂“布線美學(xué)”���,更要熟知電氣性能、制造可行性及后期調(diào)試的需求��。

深圳宏力捷電子專注電路板設(shè)計(jì)多年,擁有經(jīng)驗(yàn)豐富的PCB設(shè)計(jì)團(tuán)隊(duì)���,擅長BGA封裝��、多層盲埋孔結(jié)構(gòu)����、高速信號完整性設(shè)計(jì)�����。只需您提供原理圖����,其余從BOM建立、器件選型��、打樣生產(chǎn)�、交付測試,我們都可一站式為您搞定�!

深圳宏力捷推薦服務(wù):PCB設(shè)計(jì)打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料